依据欧盟施行的个人资料保护法,我们致力于保护您的个人资料并提供您对个人资料的掌握。

按一下「全部接受」,代表您允许我们置放 Cookie 来提升您在本网站上的使用体验、协助我们分析网站效能和使用状况,以及让我们投放相关联的行销内容。您可以在下方管理 Cookie 设定。 按一下「全部接受」即代表您同意採用目前的设定。

1-1. 请使用示波器或频率计测量晶振两端输出的讯号。 如果没有讯号输出,请依照步骤1-1至步骤1-4执行检查。 若晶振输出端(Xout)有讯号输出,但输入端(Xin)无讯号输出,请依照步骤1-5至步骤1-6检查晶振。

1-2. 请卸下晶振并使用专业测试机测试其频率和负载电容,看看它们是否振动并符合您的规格。 您也可以将其发送给您的供应商,让他们为您进行测试。

1-3. 如果出现以下情况,晶振不振动,负载电容与您的规格不符,或者当前频率与您的目标频率差距较大,请将晶振寄给您的供应商进行品质分析。 如果频率和负载电容符合您的规格,我们将需要进行等效电路测试。

1-4. 等效电路测试

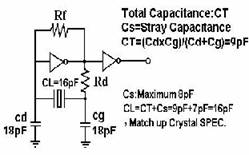

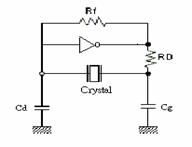

1-4-1. 一般来说,微处理器的振盪电路源自于科尔皮兹电路,如下所示: 图片1 Cd和Cg是外部负载电容,已内建在晶片组中。 (请参阅晶片组规格) Rf为回授电阻,200KΩ~1MΩ。 它通常是内建在晶片组中。 Rd为限流电阻,阻值为470Ω~1KΩ。 一般电路不需要这个电阻,只有高功率电路才需要这个电阻。

1-4-2. 一个稳定的振盪电路需要负电阻,其阻值至少应为晶振电阻的5倍。 可以写成|-R| > 5 卢比。 例如,要获得稳定的振盪电路,当晶振电阻为40Ω时,IC的负阻值必须在–200Ω以下。

1-4-3. 「负阻」是评价振盪电路好坏的标准。 在某些情况下,如老化、热变化、电压变化等,如果“Q”值较低,电路可能不会振盪。 因此,请按照以下说明测量负电阻 (-R ) 非常重要:

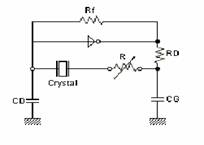

将电阻(R)与晶体串联 从振盪起始点到终止点调节R的值。 测量振盪期间的 R 值。 您将能够获得负电阻值|–R| = R + Rr,Rr = 晶体电阻。 附: 连接电路的杂散电容可能会影响测量值。

1-4-4. 如果晶振参数正常,但在振盪电路中工作不稳定,则需要检查IC的阻值是否太低,无法驱动电路。 如果是这样的话,我们可以透过三种方法来改善这种情况: 降低外部电容(Cd和Cg)的值,并採用负载电容(CL)较低的其他晶体。 採用电阻 (Rr) 较低的晶体。 测量振盪期间的 R 值。 採用Cd和Cg不等值的设计。 我们可以增加Cd(Xout)的负载电容,减少Cg(Xin)的负载电容,以提高Xin输出的波形幅度,用于其后端电路。

1-5. 当Xout有讯号输出而Xin没有讯号输出时,代表后电极后端电路的功耗极大。 我们可以在电路的输出与其后电极之间添加一个缓冲器来驱动后端电路。

1-6. 除了上述1-1 ~ 1-5的方法外,您还可以按照步骤1-4-4中的三种方法进行操作。 如果无法解决您的问题,请联络晶体或IC制造商的现场应用工程师以获得进一步的协助。

2-1. 请使用示波器或频率计数器测量晶振两端的讯号,如果频率不在规格范围内且输出波形幅度不够(例如超过+/- 200ppm),请依照步骤2-3至步骤 2-5处理。

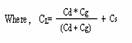

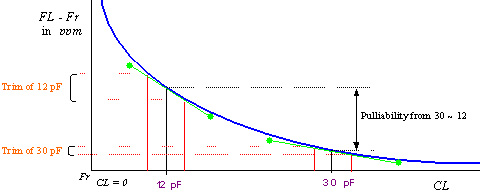

2-2. 电容与频率的关系公式如下: FL = FR * ( 1 + C1 / 2 * ( C0 + CL) ) 其中 此曲线表示电容变化随频率变化的变化(频率可驱动性):

FL = FR * ( 1 + C1 / 2 * ( C0 + CL) ) 其中 此曲线表示电容变化随频率变化的变化(频率可驱动性):

如果频率计数器测得的频率高于目标频率,则应增加电容值(CL,或Cd&Cg)以将频率降低至目标频率,反之亦然。 请检查调整频率后波形幅度是否有改善。 如果有所改善,则表示电路的原始设计没有调谐到晶体的最佳谐振点。 调整谐振点后,晶体应能正常运作。

2-3. 如果频率非常接近目标频率但波形幅度没有改善,我们可以透过以下三种方法来改善:

方法1:降低外部电容(Cd、Cg)值,採用负载电容(CL)较低的晶振。

方法2:採用电阻(Rr)较低的晶振。

方法3:採用Cd、Cg不等值设计。 我们可以增加Cd(Xout)的负载电容,减少Cg(Xin)的负载电容,以提高Xin输出的波形幅度,用于其后端电路。 建议您採用以上方法,既节省成本又确保安全

2-4. 请使用频率计数器测量晶振,以确保波形振幅改善后调整后的频率仍符合原始规格。 如果频率不符合规格,请根据您的目标频率採用合适 CL 值的晶振。

2-5。 如果频率远高于目标频率,请採用较低 CL 的晶体,反之亦然。

3-1. 针对频率输出偏差超限的问题,可以透过以下方法来改善:

方法1: 调整外部电容 Cd 和 Cg 的值。 如果频率计数器测量的频率高于目标频率,我们应该增加外部电容CL(或Cd和Cg的值),以将频率降低到我们的目标频率,反之亦然。

方法2: 採用不同电容(CL)值的晶体。 如果频率远高于目标频率,则採用电容较小的晶体,反之亦然。

3-2. 请在採用正确的电容并将频率调整到目标值后,使用示波器检查波形振幅是否正常。 当外接电容导致波形幅度缩小的情况下,请採用方法2调整频率(减少外接电容,採用电容值较小的晶振)。

4-1. 下面的曲線代表了晶體的電阻特性:

晶體有多種振動模式,如基波、三階泛音、五階泛音…等。當採用基波模式時,晶體的電阻最低,這意味著晶體最容易振盪。 當採用第三音模式時,必須利用放大電路將基模的頻率回授降低到小於第三音模式的程度。 因此,如果頻率僅為目標頻率的三分之一,則應檢查是否使用了放大電路或其設定值是否足夠,因為電路環境適合基頻模式而不是第三音模式。

4-2. 如果不使用放大電路或放大電路設定值不夠,電路可能不會振盪。

4-3. 基本模式與第三音模式的應用如下:

a. 基本模式的應用

b. 第三音模式的應用

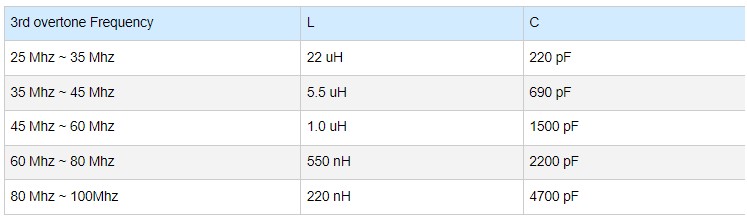

4-4. 下表為Third-Tone模式下不同頻率下L、C的匹配值:

5-1. 这个问题出现的几率比较小。 请判断三音模态的频率回授是否因放大电路的原因而大于基模模态的回授。 当放大电路内建于晶片组时,可能会出现此问题。 为了解决这个问题,请採用第三音模式晶振。

5-2. 此外,三音模式放大电路设计不当,也可能导致电路以五音模式振盪或不振盪。

7-1. 请使用频谱分析仪识别中断讯号的频率。 我们可以根据出现的频率来找出问题所在。

7-2. 如果是电源交流讯号,请检查电源接地和讯号接地是否悬空。 如果不是请改为浮动。

7-3. 若讯号频率较高,请採用以下方法: 使用水晶外壳作为接地。 採用C0较小的晶体。 增加电路外部电容Cd和Cg,并採用负载电容CL更高的晶振。

7-4. 如果上述方法无法解决您的问题,请检查週边电路和PCB佈局。 如果两者都正常,请要求IC制造商调查其晶片组设计对未知讯号的反应。 改变週边电路的设计只能缓解问题,而无法完全解决问题。 通常。 找出晶片组设计的问题并解决它是最好的。

9-1. 请使用示波器或频率计测量晶体两端的讯号。 请依照步骤9-1至9-4进行测试。 当Xin有讯号输出但波形幅度较小时,请依步骤2-1~2-5进行测试。

9-2. 请卸下晶振并使用专业测试机测试其频率和负载电容,看看它们是否振动并符合您的规格。 您也可以将其发送给您的供应商,让他们为您进行测试。

9-3. 如果出现以下任何一种情况,例如晶振不振动、负载电容与您的规格不符、或当前频率与您的目标频率差距过大,请将晶振寄给您的供应商进行品质分析。

9-4. 如果频率和负载电容满足您的规格并且晶体通过DLD测试,我们将需要进行等效电路测试。 请参考步骤1-4~1-6。

9-5。 如果晶体未通过 DLD 测试,请将其发送给您的供应商进行品质分析以进一步改进。

10-1. 拆下晶体并使用热测试机测试其频率和电阻,看看是否有振盪并符合规格。 您也可以将其发送给晶振供应商进行测试。 (热测试点间隔至少10℃/1个测试点)

10-2. 如果晶振在工作温度下的电阻和频率超出规格,请将晶振送至制造商进行品质分析并进一步改进。

10-3. 在晶振通过热测试的情况下,请检查振盪电路和其他元件的特性(如外部电容的温度特性、晶片电路的温度特性等。)。

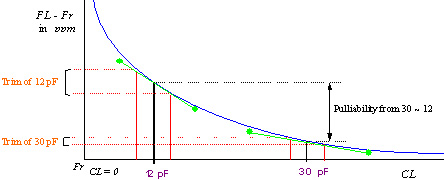

11-1. 如下图所示,VCXO电路的电容与驱动能力呈负相关,即电容越小,频率牵引范围(FL-Fr)越大,反之亦然。 /由于VCXO电路的电容是由压敏电阻控制的,所以我们可以使用电容值较小的压敏电阻或调节范围较宽的压敏电阻来扩大频率驱动范围。

11-2. 除了外部电路调整外,晶体参数的特性也会影响频率驱动范围。 其参考参数有Trim Sensitivity(TS)、C0/C1(r)、C1、C0等。各参数与频率驱动力的关系如下: C0↑ , C1↑, C0/C1(r)↓ , TS↑ , 驱动力 ↑

11-3. 如果频率驱动范围不够,我们还可以调整晶体的规格以满足目标范围。

11-4. 当由于驱动范围不对称而导致一侧驱动力不够而另一侧驱动力太大时,我们可以调整晶振的负载电容(CL),使其达到对称且两侧驱动力足够。